SiT1572

PRELIMINARY

μPower, Ultra-Small 32.768 kHz ±50 ppm Oscillator

#### **Features**

- 32.768 kHz µPower oscillator

- ±10 PPM Initial tolerance, ±50 ppm over temperature

- Smallest Footprint: 1.2 mm<sup>2</sup>

- 1.5 x 0.8 mm CSP

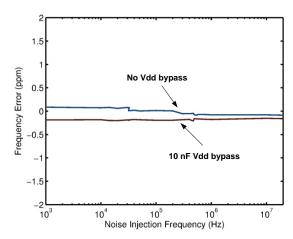

- No external bypass cap required

- Output drives multiple loads and eliminates discrete XTALs

- Improved stability reduces system power with fewer network timekeeping updates

- Ultra-low power: 4.5 µA

- Supply voltage range: 1.62V to 3.63V

- Operating temperature ranges: -40°C to +85°C

- Pb-free, RoHS and REACH compliant

# **Applications**

- Health and wellness monitors

- Wireless connectivity sleep clock

- ULP input devices

- RTC reference clock

## **Electrical Specifications**

## **Table 1. Electrical Characteristics**

Conditions: Min/Max limits are over temperature, Vdd = 1.8V ±10%, unless otherwise stated. Typicals are at 25°C and Vdd = 1.8V.

| Parameter                                | Symbol  | Min. | Тур.   | Max.      | Unit              | Condition                                                                 |  |  |  |

|------------------------------------------|---------|------|--------|-----------|-------------------|---------------------------------------------------------------------------|--|--|--|

| Frequency and Stability                  |         |      |        |           |                   |                                                                           |  |  |  |

| Output Frequency                         | Fout    |      | 32.768 |           | kHz               |                                                                           |  |  |  |

| Total Frequency Stability <sup>[1]</sup> | F_stab  | -10  | 1      | 10        | ppm               | T <sub>A</sub> = 25°C                                                     |  |  |  |

|                                          |         | -50  |        | 50        | ppm               | $T_A = -40$ °C to +85°C                                                   |  |  |  |

| First Year Frequency Aging               | F_aging |      | ±1     |           | ppm               | T <sub>A</sub> = 25°C                                                     |  |  |  |

| Jitter Performance                       |         |      |        |           |                   |                                                                           |  |  |  |

| Period Jitter                            | PJ      |      | 2.5    | 4         | ns <sub>RMS</sub> | Cycles = 10,000, Per JEDEC standard 65B                                   |  |  |  |

| Supply Voltage and Current Consumption   |         |      |        |           |                   |                                                                           |  |  |  |

| Operating Supply Voltage                 | Vdd     | 1.62 | 1.8    | 3.63      | <b>V</b>          |                                                                           |  |  |  |

| No Load Supply Current                   | ldd     |      | 4      | 5.3       | μA                | Vdd = 1.8V                                                                |  |  |  |

| Start-up Time at Power-up                | t_start |      | 135    | 300       | ms                | Measured when supply reaches 90% of final Vdd, to the first output pulse. |  |  |  |

|                                          |         |      | Opera  | ting Temp | erature Rar       | nge                                                                       |  |  |  |

| Operating Temperature Range              | Op_Temp | -40  |        | 85        | °C                |                                                                           |  |  |  |

|                                          |         |      |        | LVCMOS    | Output            |                                                                           |  |  |  |

| Output Rise/Fall Time                    | tr, tf  |      | 9      | 20        | ns                | 10-90% (Vdd), 15 pF Load.                                                 |  |  |  |

| Output Clock Duty Cycle                  | DC      | 45   |        | 55        | %                 |                                                                           |  |  |  |

| Output Voltage High                      | VOH     | 90%  |        |           | Vdd               | Ι <sub>ΟΗ</sub> = -1 μΑ                                                   |  |  |  |

| Output Voltage Low                       | VOL     |      |        | 10%       | Vdd               | I <sub>OL</sub> = 1 μA                                                    |  |  |  |

#### Note:

Relative to 32.768 kHz, includes initial tolerance, over temp stability, 3x reflow, Vdd range, board-level underfill, and 20% load variation. Tested with Agilent 53132A frequency counter. Measured with 100 ms gate time for accurate frequency measurement.

PRELIMINARY

## **Table 2. Pin Description**

| CSP<br>Pin | Symbol  | I/O                    | Functionality                                                                                                                                                                                               |

|------------|---------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NC      | Internal Test          | No Connect. Leave floating. Pin 1 is for internal testing and is designed to be left floating.                                                                                                              |

| 2          | CLK Out | OUT                    | 32.768 kHz, LVCMOS compatible output. Drive strength is sufficient to drive multiple low-power loads.                                                                                                       |

| 3          | Vdd     | Power Supply           | Operates from nominal supply voltages between 1.8V to 3.3V. Under normal operating conditions, Vdd does not require external bypass/decoupling capacitor(s). SiT1572 includes on-chip filtering capacitors. |

| 4          | GND     | Power Supply<br>Ground | Connect to ground.                                                                                                                                                                                          |

# NC 1 4 GND CLK Out 2 3 VDD

Figure 1. Pin Assignment

## **Table 3. Absolute Maximum Limits**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                          | Test Condition       | Value            | Unit |

|----------------------------------------------------|----------------------|------------------|------|

| Continuous Power Supply Voltage Range (Vdd)        |                      | -0.5 to 4.0      | V    |

| Continuous Maximum Operating Temperature Range     |                      | 105              | °C   |

| Short Duration Maximum Operating Temperature Range | ≤ 30 minutes         | 125              | °C   |

| Human Body Model (HBM) ESD Protection              | JESD22-A114          | 2000             | V    |

| Charge-Device Model (CDM) ESD Protection           | JESD22-C101          | 750              | V    |

| Machine Model (MM) ESD Protection                  | JESD22-A115          | 300              | V    |

| Latch-up Tolerance                                 |                      | JESD78 Compliant |      |

| Mechanical Shock Resistance                        | Mil 883, Method 2002 | 20,000           | g    |

| Mechanical Vibration Resistance                    | Mil 883, Method 2007 | 70               | g    |

| 1508 CSP Junction Temperature                      |                      | 150              | °C   |

| Storage Temperature                                |                      | -65 to 150       | °C   |

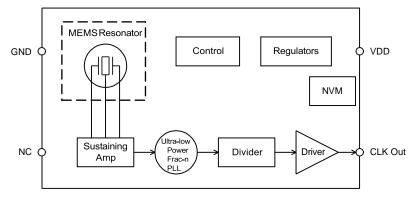

# **System Block Diagram**

Figure 2. SiT1572 Block Diagram

PRELIMINARY

# Description

The SiT1572 is an ultra-small, micropower, 32.768 kHz oscillator in a CSP-4 package. Typical supply current is 4.5  $\mu$ A under no load condition.

SiTime's MEMS oscillator consists of a MEMS resonator and a programmable analog circuit. SiT1572 MEMS resonator is built with SiTime's unique MEMS First™ process. A key manufacturing step is EpiSeal™ during which the MEMS resonator is annealed with temperatures over 1000°C. EpiSeal™ creates an extremely strong, clean, vacuum chamber that encapsulates the MEMS resonator and ensures the best performance and reliability. During EpiSeal™, a poly silicon cap is grown on top of the resonator cavity, which eliminates the need for additional cap wafers or other exotic packaging. As a result, SiTime's MEMS resonator die can be used like any other semiconductor die. One unique result of SiTime's MEMS First and EpiSeal™ manufacturing processes is the capability to integrate SiTime's MEMS die with a SoC, ASIC, microprocessor or analog die within a package to eliminate external timing components and provide a highly integrated, smaller, cost-effective solution to the customer.

# Frequency Stability

The SiT1572 oscillator is Factory trimmed to 32.768 kHz at room temperature and internally compensated over temperature. The result is a very accurate oscillator at room temperature and over temperature. Unlike quartz crystals that have a classic tuning fork parabola temperature curve with a 25°C turnover point with a 0.04 to 0.06 ppm/°C² temperature coefficient, the SiT1572 error is corrected over temperature with an active temperature correction circuit. The result is <±50 ppm frequency variation over the -40°C to +85°C temperature range.

When measuring the output frequency of SiT1572 with a frequency counter, it is important to make sure the counter's gate time is >100 ms. Shorter gate times may lead to inaccurate measurements.

PRELIMINARY

# **Typical Operating Curves**

(T<sub>A</sub> = 25°C, Vdd = 1.8V, unless otherwise stated)

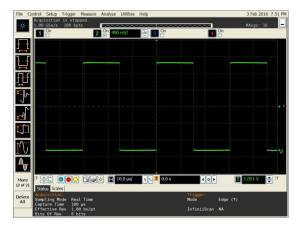

Figure 3. LVCMOS Output Swing (Vdd=1.8V)

Figure 4. Power Supply Noise rejection (PSNR)

PRELIMINARY

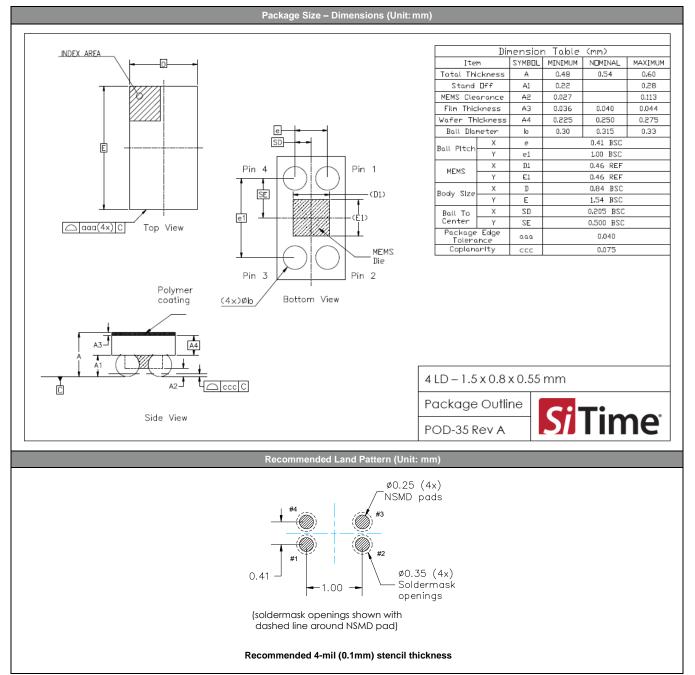

## **Dimensions and Patterns**

# **Manufacturing Guidelines**

- 1) No Ultrasonic or Megasonic cleaning: Do not subject SiT1572 to an ultrasonic or megasonic cleaning environment. Permanent damage or long term reliability issues may occur.

- 2) Applying board-level underfill and overmold is acceptable and will not impact the reliability of the device.

- 3) Reflow profile, perJESD22-A113D.

- 4) The SiT1572 CSP includes a protective, opaque polymer top-coat. If the SiT1572 will see intense light, especially in the 1.0-1.2μm IR spectrum, we recommend a protective "glob-top" epoxy or other cover to keep the light from negatively impacting the frequency stability.

- 5) For additional manufacturing guidelines and marking/tape-reel instructions, refer to SiTime Manufacturing Notes.

PRELIMINARY

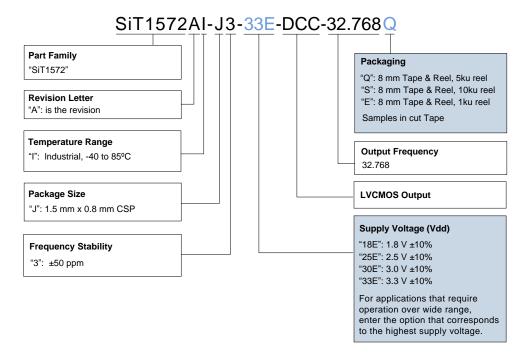

# **Ordering Information**

PRELIMINARY

#### **Table 4. Revision History**

| Version | Release Date | Change Summary      |

|---------|--------------|---------------------|

| 0.9     | 01/24/2018   | Preliminary Release |

SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation 2018. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.